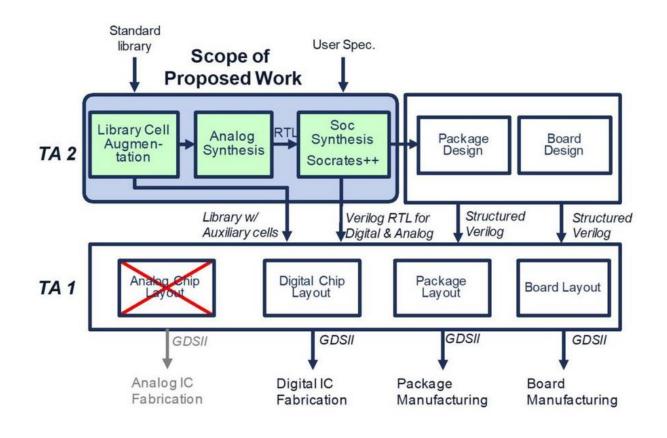

# FASoC: FULLY AUTONOMOUS SoC SYNTHESIS

# FASoC/IDEA FLOW TUTORIAL (GF12LP)

An In-Depth Guide to Your First FASoC Design

# Overview

This tutorial serves as a guide to a new user of the IDEA/FASoC program and will guide you through all of the steps required to get your first design tapeout ready. There is also useful information suited for people outside of IDEA/FASoC such as general information about working in fin-FET technologies like GF12lp and working in GitHub.

> Michels, Noah nmichels@umich.edu

# Table of Contents

| Getting Started                          | 2  |

|------------------------------------------|----|

| Overall Steps to Complete                | 3  |

| Useful Locations                         | 4  |

| Working in GF12 and Fin-FET Technologies | 4  |

| Extra GF12 Layout info:                  | 7  |

| AUX Cell File Generation                 |    |

| .sp:                                     |    |

| .cdl:                                    | 10 |

| abstract & .lef:                         | 11 |

| .gds:                                    | 17 |

| .lib:                                    | 17 |

| FASoC Block Generator                    |    |

| ./                                       |    |

| ./blocks/                                |    |

| ./src/                                   |    |

| ./scripts/dc/                            |    |

| ./scripts/innovus/                       | 19 |

| Finishing Up                             | 19 |

| Top-Level for Tapeouts                   |    |

| ./                                       |    |

| ./fasoc_soc/soc_top/                     |    |

| ./src/ & ./scripts/dc/                   |    |

| ./scripts/innovus/                       |    |

| Verifying Design                         |    |

| Working with GitHub                      |    |

| Merging Changes                          |    |

| Pushing Final Changes                    |    |

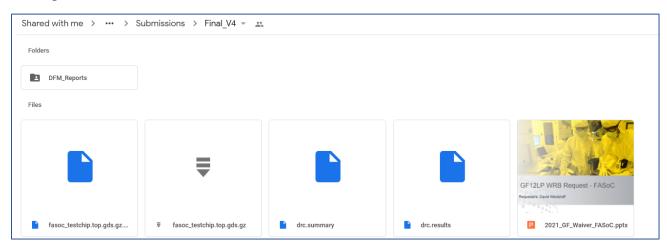

| Final Tapeout Upload                     |    |

| Appendix                                 |    |

|                                          |    |

# **Getting Started**

*Note:* Some file locations may not be general enough to be directly applicable to your design, so be sure to keep your working directory in mind. Also know that some file locations or file structures may have changed since this document was first made. Feel free to reach out to one of the FASoC members for help on first setup or any questions you may have.

The first step toward making your design, is to setup your working directory for the current technology you are working in, which for the purpose of this tutorial will be GF12lp. It is probably best to just copy the directory of another FASoC student. For now, lets use my directory as an example. There are probably many files you don't need from this directory, so if you want to copy only the necessary files that is fine too. Also before doing any of this be sure you have gotten access to the FASoC directories and the PDK files.

\$cp -r /n/Marquette/v/nmichels/GF12 ~/GF12

Great! The GF12 directory will be where you create your initial schematics and do your first tests of your design. It will also be the directory where you create you work to generate your aux cells.

Next let's go ahead and setup your FASoC working directory in your home directory. This directory is going to be a copy of the current GitHub master branch and will be where you will do the traditional FASoC work such as making your automated design (this will be covered in more detail later, so don't worry too much about this for now). Also before doing this step be sure you have been given access to the FASoC GitHub.

\$cd

\$mkdir fasoc

\$cd fasoc

\$git clone --recursive git@github.com:idea-fasoc/fasoc.git

\$cd fasoc/private

\$git checkout master

\$git submodule update --recursive --init

Now we will go ahead and setup your block generator within the fasoc directory. You won't be using this much until later, but let's go ahead and get it out of the way.

```

$cd ~/fasoc/private/generators

$mkdir ignore_[BLOCK_NAME]

```

There is a lot that goes into one of the generator directories, so for now let's just copy one of the other blocks' subdirectories.

```

$cd ~/fasoc/private/generators

$cp -r pll-gen/gf12lp/flow_dco/* ./ignore_[BLOCK_NAME]

```

We will worry about actually changing all of the files in your new generator directory later, but for now we have a good jumping off point.

Last thing is you will want to get someone's ".tcshrc" file for loading all of the necessary modules when working in the fasoc directories. For now, we will just use mine again. Can change file name if you don't want to overwrite your current ".tcshrc".

\$cp /n/Marquette/v/nmichels/.tcshrc ~/.tcshrc

Nice! Now that we are setup, we will go over the overall steps we need to complete to get your design ready.

# Overall Steps to Complete

*Note:* Everything through step 2.b will be done in GF12 directory and the rest will take place in fasoc generator directory. Can focus on just getting on design to work for now, and worry more about auto generation later. Also note that there won't be a section on creating/testing design schematic in Virtuoso, as it is assumed that you already know how to do this (still feel free to reach out with questions if having trouble).

- 1. First step is to make design in GF12lp

- a. Just worry about schematic initially, then focus on the layout of aux cells

- i. Goal is to use standard cells, so don't use rf\_fets for basic components

- ii. If standard cell doesn't exist for part, make custom std cell (AUX cell) that meets normal std cell sizing (equal height, and int. multiple of width)

- b. After schematic made, run sims and optimize

- c. Once optimized, test layout to get idea of how things will be placed

- d. GF12lp has many more rules (finfet), so if problem takes >1hour, ask for help

- 2. Now break overall design into smaller AUX cells (hopefully considered this while making original)

- a. Aux cells should meet standard cell sizing requirements (other than caps/inductors/resistors)

- b. Generate files needed for AUX cells (see AUX Cell File Generation Section)

- c. Make Verilog files defining IO for each of these aux cells

- d. Make Verilog top level which defines connections between blocks

- 3. Next Synthesize design

- a. Synthesis scripts located in ./scripts/dc/

- b. make synth

- i. check results/dc/design\_name.mapped.v

- ii. Note that blank connectivity means block is connecting to power/gnd. Power connections are defined in Innovus

- 4. Next APR design

- a. APR scripts located in /scripts/innovus/

- b. Also have to specify placements for blocks in custom\_place.tcl

- c. There are series of "stages" for APR. "stage" runs all previous "stages" if not run yet.

- d. make "stage" for stage = init, place, cts, postcts\_hold, route, postroute, signoff

- i. Also have make debug\_"stage"

- 5. LVS & DRC

- a. Focus on LVS first, as this is quicker and DRC will likely have issues

- b. make lvs; make debug\_lvs

- c. make drc; make debug\_drc

- 6. Sims

- a. Use Finesim/HSPICE to perform sims

- i. Need custom python script to generate PEX results and post-PEX sims

#### 7. TOP LEVEL & PADS....

a. This will be covered later, for now just focus on getting through block generation

# **Useful Locations**

Recommend alias to quickly access some of these files, especially design manual. If you copy my .bashrc/.tcshrc, then you will have some already.

Tool Documentation: Most files found in /usr/caen/ for tool information (Ex: Innovus, finesim, hspice)

**Technology Documentation:** Most files found in /afs/eecs.umich.edu.edu/kits/ for pdk information. Documents below are for GF12lp, but can give idea of where to look if using a different technology.

- Design Manual: /afs/eecs.umich.edu/kits/GF/12LP/tapo\_V1.0\_4.1/source/12LP\_Rev1.0\_4.0.pdf

- STD Cells Rules/Info:

- $/afs/eecs.umich.edu/kits/ARM/GF12LP/arm/gf/12lp/platform\_userguide/r0p0/doc/sc\_12lp\_doc\_userguide.pdf$

- STD Cell Files: /afs/eecs.umich.edu/kits/ARM/GF12LP/arm/gf/12lp/sc10p5mcpp84\_base\_rvt\_c14/r0p0/

- PAD Info: /afs/eecs.umich.edu/kits/ARM/GF12LP/arm/gf/12lp/io\_gppr\_t18\_mv10\_mv18\_fs18\_rvt\_dr/r1p0/

# Working in GF12 and Fin-FET Technologies

*Note:* This section will cover just some general tips and tricks for working in GF12 and other Fin-FET technologies. If you are already familiar with this type of work, you can skip this section and focus on the stuff relating more to FASoC.

Before working in your GF12 directory, be sure to source the .bashrc file. Some differences between two .bashrc files.

\$source .bashrc\_pre\_gf12\_bkp

or

\$source .bashrc\_gf12

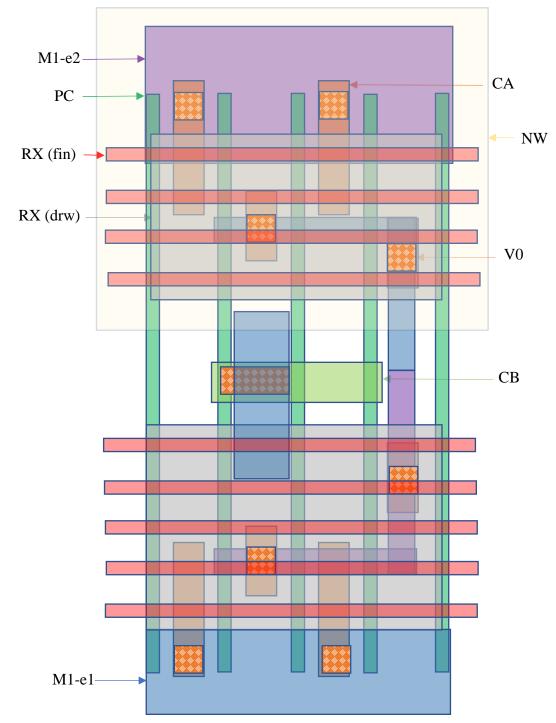

First thing we will cover is just some general layout explanations for this PDK. All of the images in this section have been generated outside of Virtuoso in an attempt to not break any NDA rules, but feel free to follow along in virtuoso to see exactly what I am talking about. Also, a quick note in case you haven't taken 427/627. In your classes you have likely been using IBM 130 and therefore are used to a lot of freedom in the layout process. In smaller technologies such as GF12, things are laid out in a grid like manner. This means things like PC are always going to go in one direction and will occur at standard intervals, so don't expect to be able to do any creative routing with this layer.

Okay, so before going into any more detail I think it is best to actually see an example. For this example, we are going to look at an inverter standard cell in the sc10p5mcpp84\_12lp\_base\_rvt\_c14 std cell library. This is the library that we were using at the time of writing this document. More information can be found in the Arm user guides which are listed in the section discussing useful locations.

The layout has a lot going on, so let's start on the next page so we can clearly see everything. I highly recommend having the design manual and the inverter standard cell open while reading through the next section so you can get a better understanding.

Consider an inverter:

M1-e1 and M1-e2 occupy same metal layer but are fabricated during different lithography steps (This double metal layer is the case for only M1-M3). NW and RX(drw) operate pretty much same as most other PDKs. CA is used to make contact to the RX(fins) whereas CB is used to make contact with the PC. To connect to upper metal layers, the CA/CB have to be followed by a V0 (a zeroth via). Note that CA doesn't have to directly contact all RX(fins) thanks to the TT layer (not shown). The TT layer occupies the same area as the RX(drw) layer and connects the CA to the RX. There is also another layer known as the TB layer (not shown) which marks the area where TT should not be placed. The TB layer overlaps the PC and prevents a short between the source and drain due to the TT layer.

The layer naming for the rest of the metal layers and vias is some variation of the following (changes depending on the exact metal stack that is being used):

CA/CB-V0-M1-V1-M2-V2-M3-J3-C4-A4-C5-A5-C6-A6-C7-CK-K1-U1-K2-KG-G1-T1-G2-W-LB

More information and a useful diagram of the metal layering can be found in the design manual.

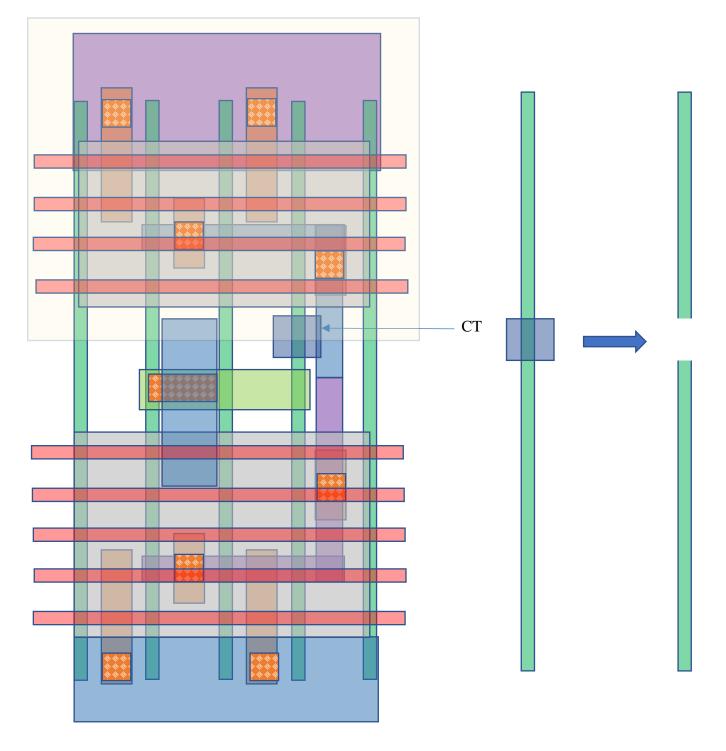

What if you need to control the gate of a PMOS without controlling the gate of a complementary NMOS? This is done by using the CT layer, which effectively cuts the PC which it is over. Thus, you should still run the PC and TB layer from the top to bottom of the std cell, but just place a CT layer between the two RX layers to prevent the gate controlling both of them (note that TB layer is not shown in this fig).

#### Extra GF12 Layout info:

- GF12 standard cells may not have schematic view initially, and there are issues with importing the .cdl files, so ask for someone who already has the files

- GF12 has many layer "purposes" (ex: drawing, e1, e2, label). In FinFET technologies, some metal layers require two masks (each mask corresponding to a separate lithography-etching process, meaning that M1-e1 is the first fabricated & then M2-e2 is the second fabricated, although they are in the same layer). In 12LP, we need e1, and e2 masks for the M1/M2/M3 layers. There are specific design rules for e1-e1, e2-e2, and e1-e2. Best to use e1/e2 layers at start rather than drawing layer for M1/M2/M3.

- Can ignore many of the other purposes for a given layer, though some are still used (ex: apmom for defining capacitor areas for mom caps)

- If you make custom aux cells, they should try to follow standard cell format

- Cell height should be 0.672 for 10p5 std cells

- $\circ$  Cell width should be 0.186+n\*0.084 for some int n

- STD cell naming convention:

- o sc9 vs sc10p5: different top power rail sizing and metal layer purpose

- INVP vs INV: "cell"P includes parasitic FETS

- INV\_X0P6"F/N/R": Cells sized for either falling, normal, or rising delays.

- If your FASoC design is having trouble routing later, can make standard cell wider by using FLTGATE layer. Just add extra PC column and cover with FLTGATE so it is not considered as a FET during LVS

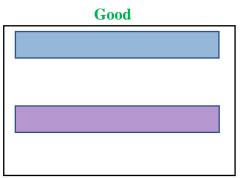

- When trying to route M1-e1 and M1-e2 in close proximity, try to do so by having them run parallel to each other. The DRC rule for spacing is more forgiving in this scenario. Example below:

Once you have got your schematic finished and AUX cells laid out, you are ready for the next section. In the next section we will work to generate files for your AUX cells that will be needed to get through the FASoC flow.

# AUX Cell File Generation

For each AUX Cell, need to generate .sp, .cdl, .lef, .gds, and .lib. This section will cover the creation of each of these file types. Even if you are familiar with how to generate these files, it is recommended you review this section as some of the files require some manual changes after they have been generated.

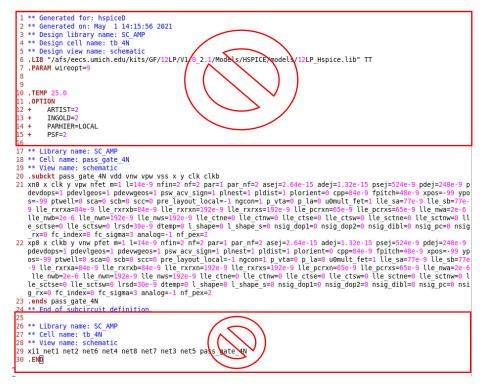

#### .sp:

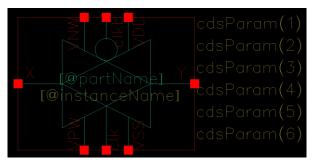

1) Generate symbol for circuit

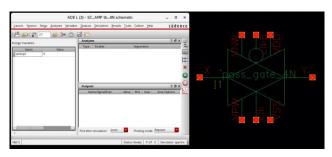

2) Add symbol to a testbench schematic and launch ADEL

3) In ADEL go to Setup -> Simulator/Directory/Host and set Simulator to hspiceD

| Launch Session                                                       | Setup Analyses                | <u>V</u> aria bles | Outputs              | Simulation   | <u>R</u> e sults | Tools       | Calibre           | Help    |          | cāder | n          |

|----------------------------------------------------------------------|-------------------------------|--------------------|----------------------|--------------|------------------|-------------|-------------------|---------|----------|-------|------------|

| 10 00 10                                                             | 💾 Design                      |                    |                      |              |                  |             |                   |         |          |       |            |

| Design Variables                                                     | 😥 Simulator/Di                | ectory/Host        | ***                  | 5            |                  |             |                   |         |          | 78×   | C. C. MILL |

| Name                                                                 | High-Perform                  |                    | tion                 | Enable       |                  | _           | Argume            | nts     | _        |       |            |

| 1 wireopt                                                            | Model Librar                  |                    |                      |              |                  |             |                   |         |          |       | 1          |

|                                                                      | Temperature                   |                    |                      |              |                  |             |                   |         |          |       |            |

|                                                                      | ≯ Stim <u>u</u> li            |                    |                      |              |                  |             |                   |         |          |       |            |

|                                                                      | Simulation Fi<br>EM/IR Analys |                    |                      |              |                  |             |                   |         |          |       | 1          |

|                                                                      | MATLAB/Sim                    |                    |                      |              |                  |             |                   |         |          |       |            |

|                                                                      | A Environment                 |                    |                      | 5            | _                |             | _                 |         |          | ? 🖥 🗙 | 1          |

|                                                                      |                               |                    |                      | me/Signal/Ex |                  | Value       | Plot              |         | Save Opt |       |            |

|                                                                      |                               |                    |                      |              |                  |             |                   |         |          |       |            |

| - 10                                                                 |                               | ×                  |                      | simulation:  | Auto             |             |                   | mode: R |          |       |            |

| >                                                                    |                               | >                  |                      |              |                  |             | Plotting          | mode: R | eplace   |       |            |

| ><br>[8(21) Simulato                                                 | /Directory/Host               |                    | Plotafter            | simulation:  | Auto             | Status      | Plotting<br>Ready | mode: R |          |       |            |

| 3<br>  <br> 8(21) Simulato<br> C                                     | noosing Simulat               |                    | Plotafter            | simulation:  | Auto             | Status      | Plotting          | mode: R | eplace   |       |            |

| BIR CI                                                               | hspiceD                       | or/Direct          | Plotafter            | simulation:  | Auto             | Status      | Plotting<br>Ready | mode: R | eplace   |       |            |

| B(21) Simulato<br>Cl<br>imulator<br>troject Directory                | hoosing Simulat               | or/Directo         | Plotafter<br>ory/Hos | simulation:  | Auto             | Status      | Plotting<br>Ready | mode: R | eplace   |       |            |

| IN 211 Simulato                                                      | hspiceD                       | or/Directo         | Plotafter<br>ory/Hos | simulation:  | Auto             | Status      | Plotting<br>Ready | mode: R | eplace   |       |            |

| 18(21) Simulato<br>Cl<br>imulator<br>Project Directory<br>flost Mode | hoosing Simulat               | or/Directo         | Plotafter<br>ory/Hos | simulation:  | Auto             | •<br>Status | Plotting<br>Ready | mode: R | eplace   |       |            |

| >                                                                    | hoosing Simulat               | or/Directo         | Plotafter<br>ory/Hos | simulation:  | Auto             | • Status    | Plotting<br>Ready | mode: R | eplace   |       | tr         |

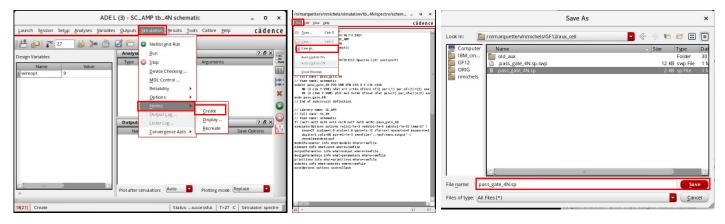

4) Go to simulation -> Netlist -> Create and save the resulting file as [filename].sp

5) Open file and delete the following portions to finish

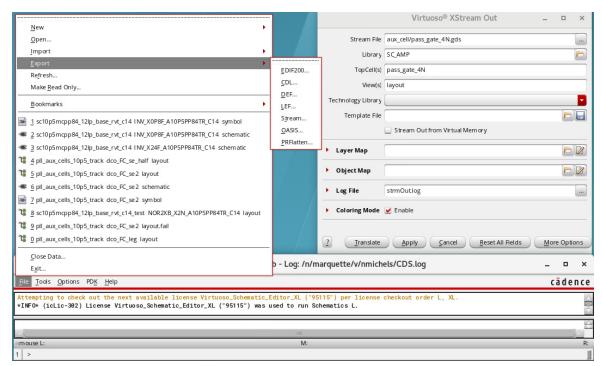

#### .cdl:

1) From Virtuoso CIW go to files -> Export -> CDL

|        | cäden                                      |

|--------|--------------------------------------------|

|        | - Log: /n/marquette/v/nmichels/CDS.log _ = |

| symbol | QASS.<br>PRFlatten_                        |

| -      | LEF<br>Syream                              |

|        | DEL"                                       |

|        | EDIF200<br>CDL                             |

|        |                                            |

|        |                                            |

|        | •                                          |

a. See example settings below: everything else left default

| Template File           |                    |                   |

|-------------------------|--------------------|-------------------|

|                         | Browse Load        | Save              |

| Design to be Netlisted  |                    |                   |

| Library Name            | SC_AMP             | (Library Browser) |

| Top Cell Name           | pass_gate_4N       |                   |

| View Name               | schematic          |                   |

| Switch View List        | auCdl schematic    |                   |

| Stop View List          | auCdl              |                   |

| Output                  |                    |                   |

| Output CDL Netlist File | netlist            | View              |

| Run Directory           |                    | Browse            |

| letlisting Mode         | 🔾 Digital 🖲 Analog |                   |

| tun in Background       | ⊻                  |                   |

| enetlist                |                    |                   |

- 2) Save output netlist file -> Save as [filename].cdl

- a. Sometimes doesn't show output netlist on first try, so may run twice

- 3) delete the following portion to finish

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 • auCdl Netlist:<br>4 • Library Name: SC AMP<br>5 • Top Cell Name: pass gate AN<br>6 • View Name: schematic<br>7 • Netlisted on: May 1 15:14:03 2021<br>9<br>10 • .BIPOLAR<br>11 • .RESPAL<br>13 • .CAPVAL<br>14 • .DIOPERI<br>15 • .DIOAREA<br>16 • .EQUATION<br>17 • .SCALE METER<br>18 • .MECGA<br>19 .PARAM<br>20<br>21                                                                                                            |  |

| <pre>23 * Library Name: SC.AMP 25 * Cell Name: pass gate 4N 26 * View Name: schematic 27 28 29 .SUBCKT pass_gate_4N VDD VNW VPW VSS X Y clk clkb 30 *.PININFO X:i clk:I clkb:I Y:0 VDD:B VNW:B VFW:B VSS:B 31 NN0 X clk Y VPW fret m=1 l=14n nf=2 fpitch=48n cpp=84n ngcon=1 p_la=0 32 + plorient=0 analog=-1.0 33 MP0 X clkb Y VMV pfet m=1 l=14n nf=2 fpitch=48n cpp=84n ngcon=1 p_la=0 34 + plorient=0 analog=-1.0 35 .ENDS 36 </pre> |  |

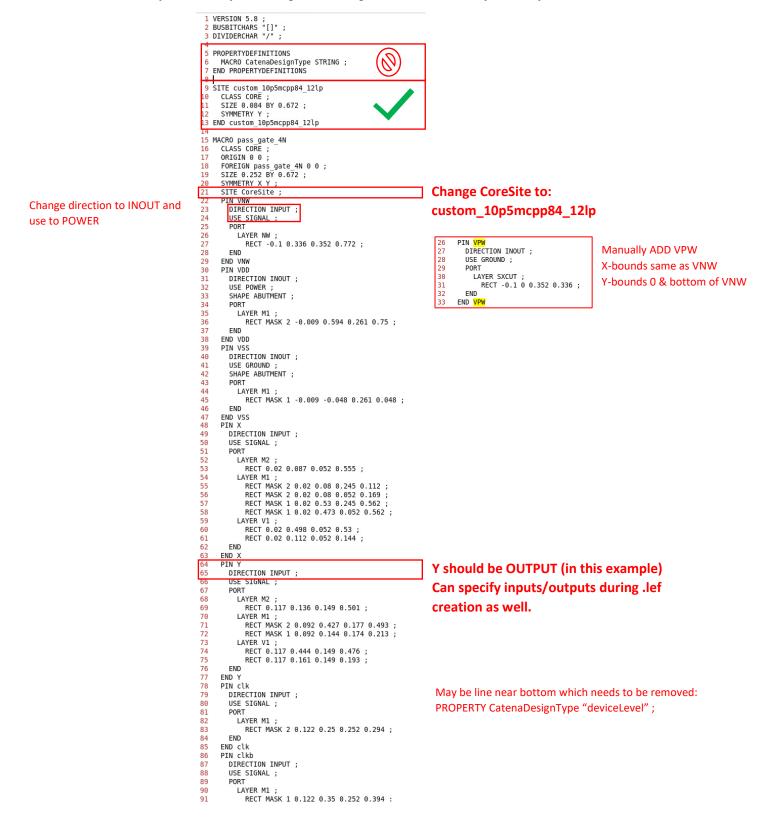

#### abstract & .lef:

- 1) Prior to exporting abstract or .lef file, need to make sure layout metal layers have mask "colors" locked

- a. Open Layout and select all metal layer of a given mask

- b. open properties (q)

- c. set mask color to 1 for e1 layer and 2 for e2 layer, then set state to lock

- d. repeat for each metal layer with masks

| Filter  |        | <b>X</b>   |       |     |                                      |           |                        |                    |       |                   |       |

|---------|--------|------------|-------|-----|--------------------------------------|-----------|------------------------|--------------------|-------|-------------------|-------|

| M1 e1   |        | <b></b>    |       |     |                                      |           |                        |                    |       |                   |       |

| AV 🔻 NV | ▼ AS   | • NS •     |       |     |                                      |           |                        |                    |       |                   | _     |

| Layer   | Purpo. | V S        |       |     |                                      |           | Edit Rectangl          | e Properties       |       |                   | ×     |

| BP      | drw    |            |       |     |                                      |           |                        |                    |       |                   |       |

| CA      | drw    |            |       |     |                                      | <         | > App                  | ily -/5 🗹 Common 5 |       |                   |       |

| CB      | drw    |            | 55558 |     |                                      |           |                        |                    |       |                   |       |

| CPP84   | drw    |            |       |     | <ul> <li>Shapes (5)</li> </ul>       | Attribute | Connectivity Parameter | Property ROD       |       |                   |       |

| CT      | drw    |            |       |     | Rectangle: M1/e1<br>Rectangle: M1/e1 |           |                        |                    |       |                   |       |

| 🗱 M1    | e1     | <b>v v</b> |       |     | Rectangle: M1/e1                     | Layer     | M1 e1                  |                    |       |                   |       |

| M1      | e2     |            |       |     | Rectangle: M1/e1                     |           |                        |                    |       |                   |       |

| M1      | label  |            |       |     | Rectangle: M1/e1                     | Left      | AS IS                  | Bottom             | AS IS |                   |       |

| M2      | e1     |            |       |     |                                      |           |                        |                    |       |                   |       |

| M2      | e2     |            |       |     |                                      | Right     | AS IS                  | Тар                | AS IS |                   |       |

| NW      | drw    |            |       |     |                                      |           |                        |                    |       |                   |       |

| NW      | label  |            |       | V . |                                      | Width     | ASIS                   | Height             | AS IS |                   |       |

| OUTLINE | drw    |            |       |     |                                      | MOTO      | oloring                |                    |       |                   |       |

| PC      | drw    |            |       |     |                                      | WIFTO     | ororing                |                    |       |                   |       |

| RC      | drw    |            |       |     |                                      |           |                        |                    |       |                   |       |

| RVT     | drw    |            |       |     |                                      | Color     | mask1Color             | State lock         |       |                   |       |

| RX      | drw    |            |       |     |                                      |           |                        |                    |       |                   |       |

| RX      | fin    |            |       |     |                                      |           |                        |                    |       |                   |       |

| SXCUT   | label  |            |       |     |                                      |           |                        |                    |       |                   |       |

| TB      | drw    |            |       |     | Describent in Commen                 |           |                        |                    |       | General (America) | 11414 |

| TT      | drw    |            |       |     | Deselect In Canvas                   |           |                        |                    | ОК    | Cancel Apply      | Help  |

| V0      | drw    |            |       |     |                                      |           |                        |                    |       |                   |       |

- 2) From working directory, run /usr/caen/icadv-12.3.500.2100/bin/abstract &

- a. If have source .bashrc\_gf12, can use absgen12 (later lefgen12)

- b. Load library you are working in

| Click -> load library                                                                                                                                          | Abstract - [no current library]                                      |        | ×    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|------|

| File Bins Cells Flow                                                                                                                                           |                                                                      | н      | lelp |

|                                                                                                                                                                |                                                                      |        |      |

| Bin         Cells           Core         0           IO         0           Corner         0           Block         0           Ignore         0              | Cell Layout Logical Pins Extract Abstract                            | Verify |      |

| Interpreter: 🔷 TcI 🔶 Skill                                                                                                                                     |                                                                      |        |      |

| 2.3-64b.500.21 , on 3.18.26<br>INFD (ABS-19023): This is the OpenAccess<br>*WARNING* LIB sc10p5mcpp84_121p_base_rvt<br>LIB sc10p5mcpn84_121p_base_rvt_c14_from | c14 from File /n/marquette/v/nmichels/GF12/cds.lib Line 46 redefines |        |      |

| abstract>                                                                                                                                                      |                                                                      |        |      |

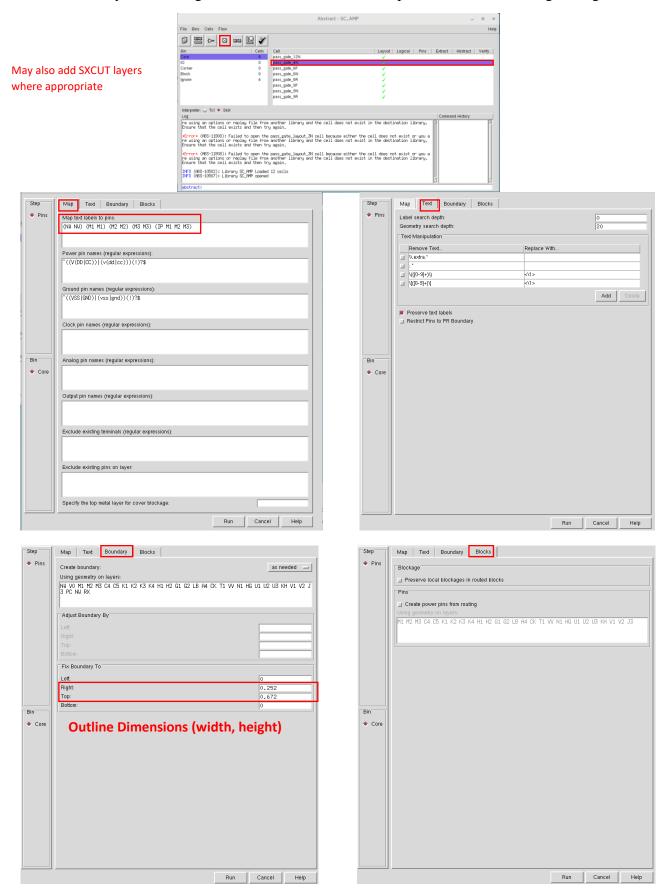

3) Select cellview you want to generate abstract for, then run "pins" with the following settings:

4) Run "Extract" with the following Settings (May also add SXCUT layers where appropriate):

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     | Abstract - SC_AMP                                                                                                            |                                               | _ 0 ×                                                                                                                                                    |                                                |                                                                  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------|

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | File Bins Cells Flow                                                                |                                                                                                                              |                                               | Help                                                                                                                                                     |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D 🕮 🗠 🛛 📾 💾 🖋<br>Bin Cells                                                          | Cell                                                                                                                         | Lavout Logical                                | Pins Extract Abstract Verify                                                                                                                             |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Core 8<br>10 0                                                                      | pass_gate_12N<br>pass_gate_4N                                                                                                |                                               |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Corner 0<br>Block 0                                                                 | pass_gate_6F<br>pass_gate_6N<br>pass_gate_6R                                                                                 | 2                                             |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ignore 4                                                                            | pass_gate_oH<br>pass_gate_9F<br>pass_gate_9N                                                                                 | 3                                             |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     | pass_gate_9R                                                                                                                 | 2                                             |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interpreter: 🗢 Tol 🔶 Skill<br>Log                                                   |                                                                                                                              |                                               | Command History                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | re using an options or replay file from<br>Ensure that the cell exists and then try | another library and the cell does not exist in t<br>y again.                                                                 | he destination libr                           | rary, 🖾 🖾                                                                                                                                                |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Error* (ABS-11908): Failed to open the<br>re using an options or replay file from   | pass_gate_layout_3N cell because either the cell<br>another library and the cell does not exist in t<br>y again.             | does not exist or<br>he destination libr      | ypu a<br>rary.                                                                                                                                           |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     | y again.<br>pass_gate_layout_3N cell because either the cell<br>another library and the cell does not exist in t<br>y again. |                                               |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ensure that the cell exists and then try                                            | andrae indrary and the cell does not exist in t<br>y again,<br>12 cells                                                      | Ne descination libr                           |                                                                                                                                                          |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INFO (A6S-10502): Library SC_AMP Loaded<br>INFO (A6S-10507): Library SC_AMP opened  | 12 00110                                                                                                                     |                                               | 1                                                                                                                                                        |                                                |                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | abstract>                                                                           |                                                                                                                              |                                               |                                                                                                                                                          |                                                |                                                                  |

| Step                                          | Signal Power Antenna General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                     | 1                                                                                                                            | Step                                          | Signal Power Antenna                                                                                                                                     | General                                        |                                                                  |

| <ul> <li>Extract</li> </ul>                   | Extract signal nets<br>Layer Assignment for Signal Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |                                                                                                                              | ↓ Pins<br>◆ Extract                           | Extract power nets<br>Layer Assignment for Power Extract                                                                                                 | tion                                           |                                                                  |

|                                               | Layer Geometry Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Connectivity Create                                                                 | Pins A                                                                                                                       |                                               | Layer Geometry Speci                                                                                                                                     |                                                | Create Pins                                                      |